- 您现在的位置:买卖IC网 > Sheet目录411 > EK43601-01 (Peregrine Semiconductor)KIT EVAL FOR 43601 RF DSA

�� �

�

PE43601�

�Product� Specification�

�Evaluation� Kit�

�The� Digital� Attenuator� Evaluation� Kit� board� was�

�designed� to� ease� customer� evaluation� of� the�

�PE43601� Digital� Step� Attenuator.�

�Direct-Parallel� Programming� Procedure�

�For� automated� direct-parallel� programming,�

�connect� the� test� harness� provided� with� the� EVK�

�from� the� parallel� port� of� the� PC� to� the� J1� &� Serial�

�header� pin� and� set� the� D0-D5� SP3T� switches� to�

�the� ‘MIDDLE’� toggle� position.� Position� the�

�Parallel/Serial� (� P� /� ?� S)� select� switch� to� the� Parallel�

�(or� left)� position.� The� evaluation� software� is�

�written� to� operate� the� DSA� in� either� Parallel� or�

�Serial-Addressable� Mode.� Ensure� that� the�

�software� is� set� to� program� in� Direct-Parallel� mode.�

�Using� the� software,� enable� or� disable� each� setting�

�to� the� desired� attenuation� state.� The� software�

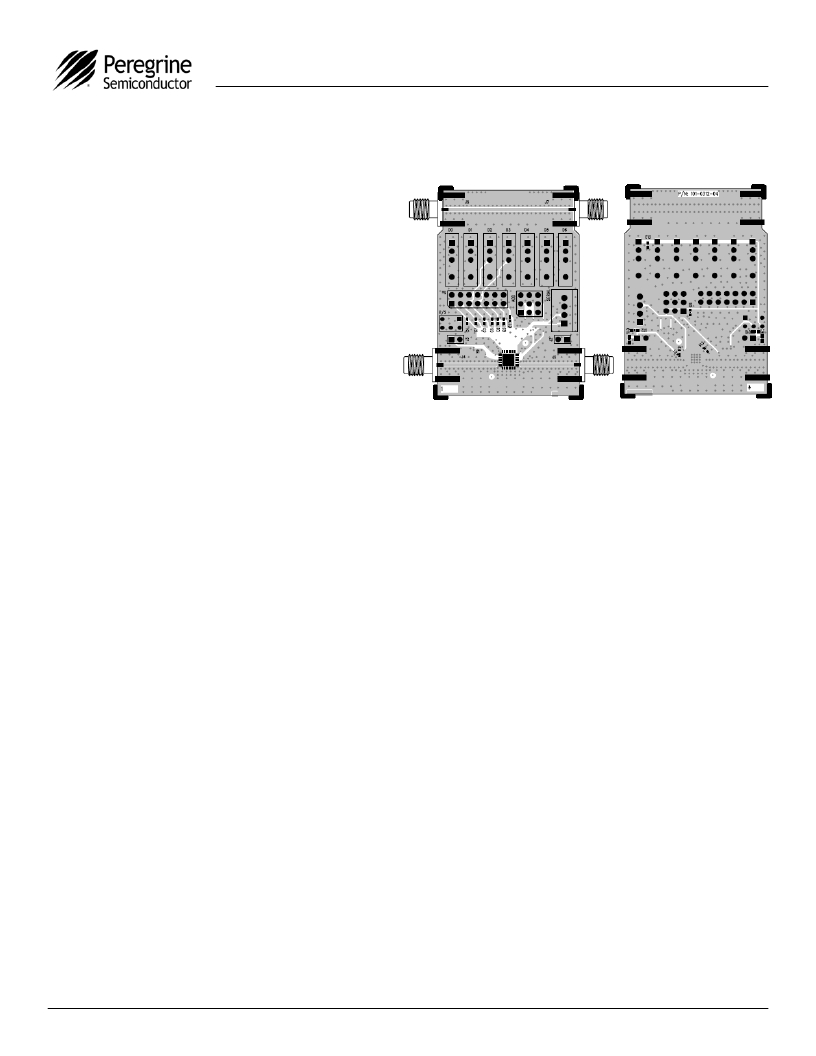

�Figure� 22.� Evaluation� Board� Layout�

�Peregrine� Specification� 101-0312�

�Note:� Reference� Fig.� 23� for� Evaluation� Board� Schematic�

�automatically� programs� the� DSA� each� time� an�

�attenuation� state� is� enabled� or� disabled.�

�For� manual� latched-parallel� programming,� the�

�For� manual� direct-parallel� programming,�

�disconnect� the� test� harness� provided� with� the� EVK�

�from� the� J1� and� Serial� header� pins.� Position� the�

�Parallel/Serial� (� P� /� ?� S)� select� switch� to� the� Parallel�

�(or� left)� position.� The� LE� pin� on� the� Serial� header�

�must� be� tied� to� logic� high.� Switches� D0-D5� are�

�SP3T� switches� which� enable� the� user� to� manually�

�program� the� parallel� bits.� When� any� input� D0-D5�

�is� toggled� ‘UP’,� logic� high� is� presented� to� the�

�parallel� input.� When� toggled� ‘DOWN’,� logic� low� is�

�presented� to� the� parallel� input.� Setting� D0-D5� to�

�the� ‘MIDDLE’� toggle� position� presents� an� OPEN,�

�which� forces� an� on-chip� logic� low.� Table� 7� depicts�

�the� parallel� programming� truth� table� and� Fig.� 21�

�illustrates� the� parallel� programming� timing�

�diagram.�

�Latched-Parallel� Programming� Procedure�

�For� automated� latched-parallel� programming,� the�

�procedure� is� identical� to� the� direct-parallel�

�method.� The� user� only� must� ensure� that� Latched-�

�Parallel� is� selected� in� the� software.�

�procedure� is� identical� to� direct-parallel� except� now�

�the� LE� pin� on� the� Serial� header� must� be� logic� low�

�as� the� parallel� bits� are� applied.� The� user� must�

�then� pulse� LE� from� 0V� to� V� DD� and� back� to� 0V� to�

�latch� the� programming� word� into� the� DSA.� LE�

�must� be� logic� low� prior� to� programming� the� next�

�word.�

�Serial-Addressable� Programming� Procedure�

�Position� the� Parallel/Serial� (� P� /� ?� S)� select� switch� to�

�the� Serial� (or� right)� position.� Prior� to�

�programming,� the� user� must� define� an� address�

�setting� using� the� ADD� header� pin.� Jump� the�

�middle� pins� on� the� ADD� header� A0-A2� (or� lower)�

�row� of� pins� to� set� logic� high,� or� jump� the� middle�

�pins� to� the� upper� row� of� pins� to� set� logic� low.� If�

�the� ADD� pins� are� left� open,� then� 000� become� the�

�default� address.� The� evaluation� software� is�

�written� to� operate� the� DSA� in� either� Parallel� or�

�Serial-Addressable� Mode.� Ensure� that� the�

�software� is� set� to� program� in� Serial-Addressable�

�mode.� Using� the� software,� enable� or� disable� each�

�setting� to� the� desired� attenuation� state.� The�

�software� automatically� programs� the� DSA� each�

�time� an� attenuation� state� is� enabled� or� disabled.�

�?2008-2009� Peregrine� Semiconductor� Corp.� All� rights� reserved.�

�Document� No.� 70-0253-05�

�│� UltraCMOS?� RFIC� Solutions�

�Page� 10� of� 13�

�Logo� updated� under� non-rev� change.� Peregrine� products� are� protected� under� one� or� more� of� the� following� U.S.� Patents:� http://patents.psemi.com�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EK43602-01

KIT EVAL FOR PE43602 RF DSA

EK43701-01

KIT EVAL FOR 43701 RF DSA

EK43702-01

KIT EVAL FOR PE43702 RF DSA

EK43703-01

KIT EVAL FOR PE43703 DSA

EK64904-01

KIT EVAL FOR 64904 NO CABLES

EK64905-11

KIT EVAL FOR 64904 W/CABLES

EKL3104

D-IMAGER 3D IMAGE SENSOR

EKL3105

3D IMAGE SENSOR-HIGH PRECISION

相关代理商/技术参数

EK43602-01

功能描述:KIT EVAL FOR PE43602 RF DSA RoHS:是 类别:RF/IF 和 RFID >> RF 评估和开发套件,板 系列:UltraCMOS™, HaRP™ 标准包装:1 系列:- 类型:GPS 接收器 频率:1575MHz 适用于相关产品:- 已供物品:模块 其它名称:SER3796

EK43701-01

功能描述:KIT EVAL FOR 43701 RF DSA RoHS:是 类别:RF/IF 和 RFID >> RF 评估和开发套件,板 系列:UltraCMOS™, HaRP™ 标准包装:1 系列:- 类型:GPS 接收器 频率:1575MHz 适用于相关产品:- 已供物品:模块 其它名称:SER3796

EK43702-01

功能描述:KIT EVAL FOR PE43702 RF DSA RoHS:是 类别:RF/IF 和 RFID >> RF 评估和开发套件,板 系列:UltraCMOS™, HaRP™ 标准包装:1 系列:- 类型:GPS 接收器 频率:1575MHz 适用于相关产品:- 已供物品:模块 其它名称:SER3796

EK43703-01

功能描述:KIT EVAL FOR PE43703 DSA RoHS:是 类别:RF/IF 和 RFID >> RF 评估和开发套件,板 系列:UltraCMOS™, HaRP™ 标准包装:1 系列:- 类型:GPS 接收器 频率:1575MHz 适用于相关产品:- 已供物品:模块 其它名称:SER3796

EK43704-11

制造商:Peregrine Semiconductor 功能描述:FREQUENCY CONTROL EVALUATION BOARD

EK43705-11

功能描述:EVAL KIT FOR RF DSA 7BIT 50OHM 制造商:peregrine semiconductor 系列:UltraCMOS?,HaRP?? 零件状态:有效 类型:衰减器 频率:50MHz ~ 8GHz 配套使用产品/相关产品:PE43705 所含物品:板 标准包装:1

EK43711-02

功能描述:EVAL BOARD FOR PE43711 制造商:peregrine semiconductor 系列:UltraCMOS?,HaRP?? 零件状态:有效 类型:衰减器 频率:9kHz ~ 6GHz 配套使用产品/相关产品:PE43711 所含物品:板 标准包装:1

EK43712-02

功能描述:EVAL BOARD FOR PE43712 制造商:peregrine semiconductor 系列:UltraCMOS?,HaRP?? 零件状态:有效 类型:衰减器 频率:9kHz ~ 6GHz 配套使用产品/相关产品:PE43712 所含物品:板 标准包装:1